パッケージファウンドリ

パッケージファウンドリ

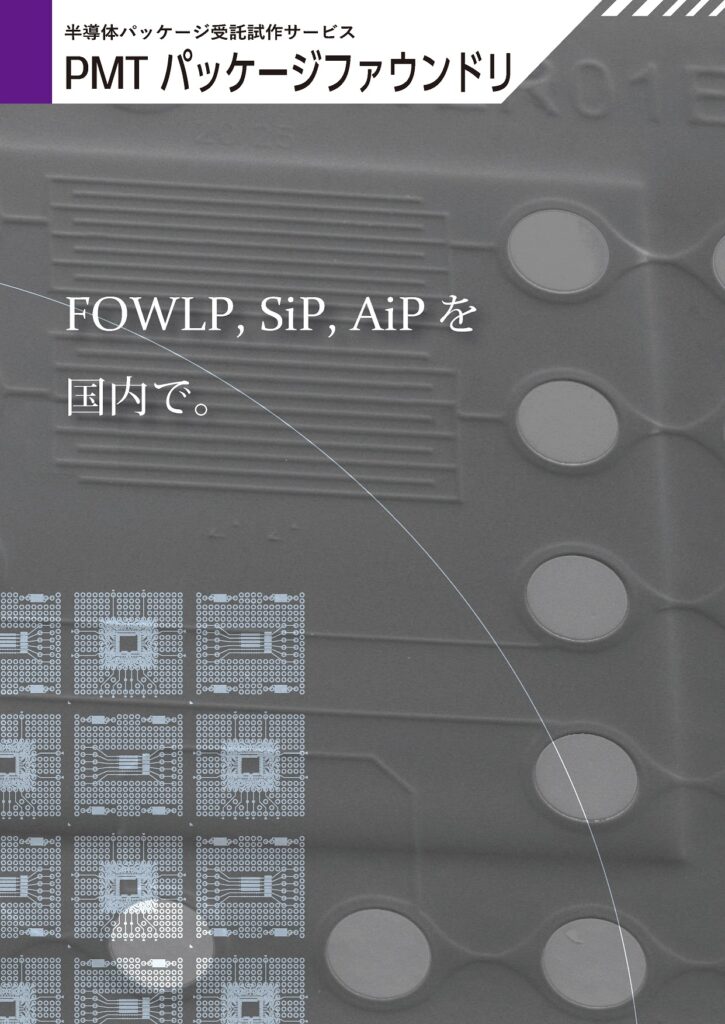

PMT Package Foundry®は、FOWLP(Fan Out Wafer Level Package)やWLCSP(Wafer Level Chip Size Package)といった、先端パッケージの少量多品種製造に特化したファウンドリサービスです。

半導体前工程技術とめっき技術を活用し、Cu再配線パッケージを作製。シリコン以外にも、SiCやGaNなど化合物半導体のパッケージ化も実績があります。

PMT Package Foundry®は、(株)ピーエムティーの登録商標です。

PMT Package Foundryのビジョン

PMT Package Foundryは、当社の新規事業として2019年に設立された、パッケージの受託製造サービスです。

半導体パッケージの中でも、FOWLP/WLCSPといった先端パッケージの試作開発に特化。チップ開発のPoC(Proof of Concept:概念実証)や製品開発のサポートを行っています。

2022年からはマクセル(株)九州事業(福岡県田川市)と連携して6インチ製造ラインの立ち上げを進めており、パッケージの試作開発はもちろん、製造キャパシティの強化を図っています。

納期・価格

ウェハ単位でご支給いただく必要はありません。

数チップからでも実装できるため、海外の OSAT や半導体研究所に比べ、低価格・短納期での対応が可能です。

設計・検証

異種機能を持つ複数の IC チップを組み合わせた異種(ヘテロジニアス)パッケージや、設計した IC チップに再配線(RDL)インターポーザを取り付けたパッケージの機能検証が可能です。

放熱・消費電力

パッケージ基板やバンプが不要なのでパッケージの低背化でき、熱抵抗の低減と放熱性の改善が望めます。

また、基板や Si チップのバンプを必要としないので配線の電気抵抗低減や信号ノイズ改善が期待できます。

プロセス

ウェハ前工程+パッケージ工程 + めっき工程のインテグレーション力によってお客様のお困りごと解決をお手伝いします。

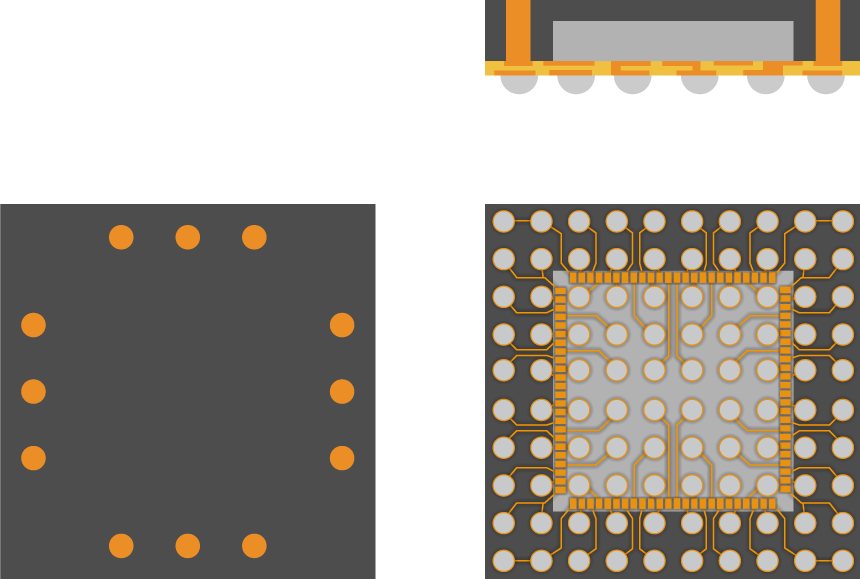

パッケージ構造比較

パッケージ構造比較

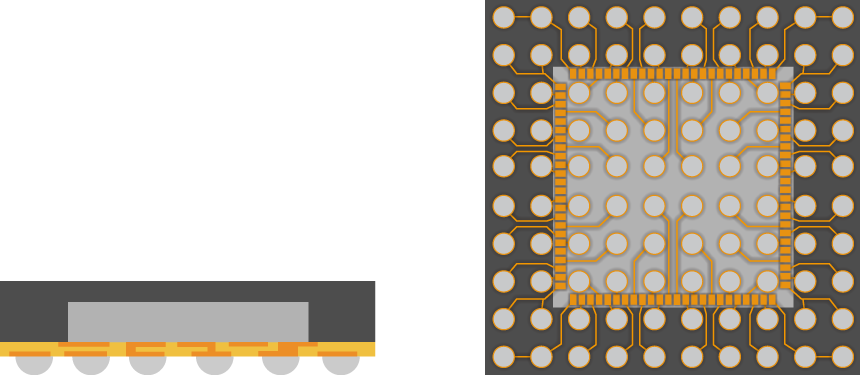

FOWLP(Fan-Out Wafer Level Package)構造は、従来のFCBGA(Flip Chip Ball Grid Array)構造に比べ、パッケージ基板やワイヤーボンディング、はんだバンプを必要としないため、小型低背化が可能になり、伝送速度が速くなります。

また、自由度のある再配線設計により任意の位置へのバンプ形成が可能になるほか、ICチップの裏面を露出させることができるため、熱抵抗の低減や放熱性の向上というメリットもあります。

様々なパッケージの試作に

様々なパッケージの試作に

PMTパッケージファウンドリでは試作専用の1インチWLPラインを有し、設計のPoCを少量のパッケージによって、短納期で行うことができます。

生産に移行するまでの中量評価から多品種少量評価までは、1インチとベースラインを同じくする6インチラインで行えるため、再度条件設定などを行う必要はありません。

下表に示す通り多様なパッケージを開発しており、今後もお客様のニーズに沿った革新的な技術開発を進めてまいります。

| 製造ライン | 1 or 6インチ製造ライン(試作/少量多品種製造/多層再配線) |

| パッケージタイプ | FOWLP/WLCSP/SiP(System-in-Package)/DSEP(両面電極パッケージ)/AiP(Antenna-in-Package)/超薄型パッケージ |

| バンプ | Cuピラーバンプ/Cuパッド/はんだバンプ |

Fan-Out 型パッケージ(FOWLP)

IC チップの入出力パッドに再配線インターポーザを接続し、基板の任意の位置への接続を可能にします。

小型化/低背化により放熱性の向上が期待できます。

Chip Scale 型パッケージ(WLCSP)

実装する半導体チップと同サイズのパッケージ。

シャトル便による個片化チップに、後付けではんだボールを搭載できます。

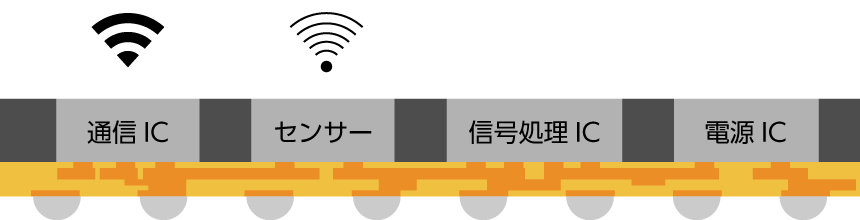

システムインパッケージ(SiP)

異種機能を持つ複数の IC を 1 つのパッケージ内でシステム化。

実装面積が小さくなるため、消費電力の低減が期待できます。

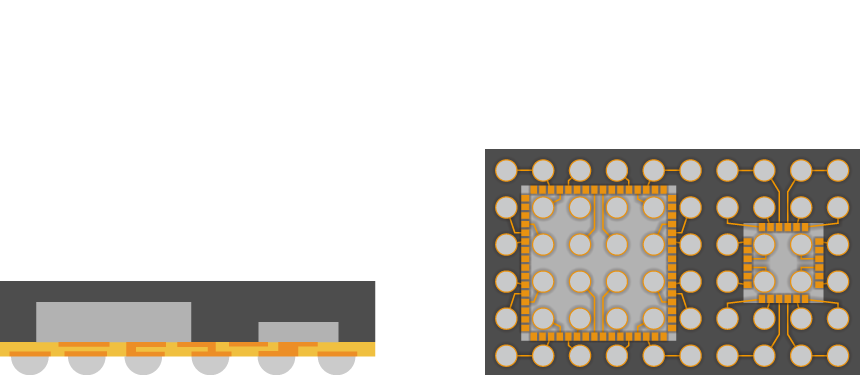

両面電極パッケージ(DSEP)

IC チップの入出力信号をパッケージ裏面から接続できるようにし、パッケージを重ねることで高機能化を図ります。

※Package on Package(ICパッケージの搭載)には対応していません

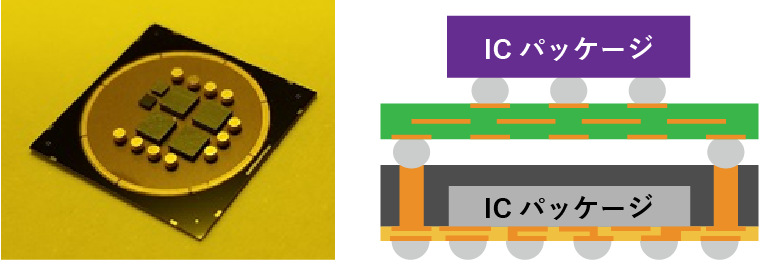

Package on Packageの事例(右)

超薄型パッケージ

パッケージ厚を10µmまで薄くすることで熱を発散しやすくし、内部の熱の滞留を防止。

ON抵抗が小さい、周波数が高いなどSiCの特性を活かしたパッケージで、小型化、高速動作、高温動作といったニーズに対応します。

ウエアラブル用パッケージとしてもスペース削減が可能です。

Cuピラーバンプ

Cuパッド、はんだバンプに加え、φ40um × t=40umのCuピラーバンプ形成が可能です。

パッケージの小型化、高集積化に対するニーズが高まる中、狭パッドピッチに対応することができます。

デザインルール

デザインルール

半導体チップやセンサーを内蔵したパッケージ構造です。

供給いただくKGD(Known Good Die)ははんだバンプ不要。外部端子ははんだボール/Cuパッドどちらでも対応可能です。

| Fan-Outモールド樹脂 再構成基板 | サイズ :φ22mm/φ150mm(*) |

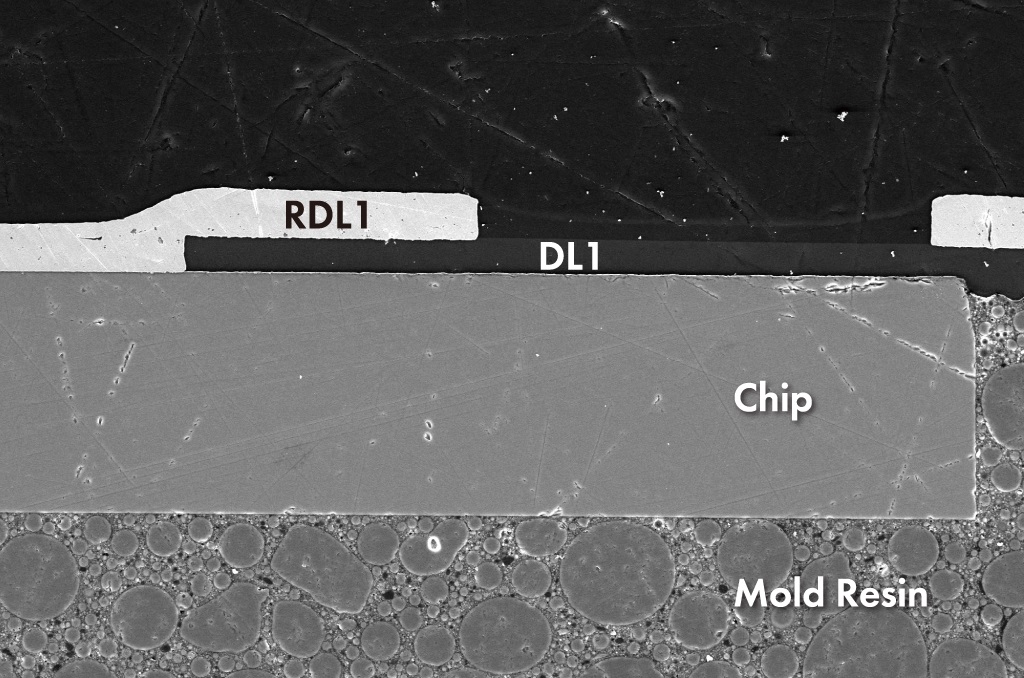

| 絶縁層(DL) | 膜厚 :3-9µm |

| 銅再配線層(Cu RDL) | 層厚 :3-15µm 層数 :最大4層 |

| L/S | 最小20µm/20µm |

| UBM | 材質 :Ni/Au |

| はんだボール | ボール径:250-500µm ピッチ :≧400µm |

(*)φ150mmは2023年10月リリース予定です。

FOWLPプロセスフロー

FOWLPプロセスフロー

PMT Package Foundryのベースラインプロセスはface-down chip-firstを採用しています。

face-up chip-firstやRDL-first、またはそれ以外の具体的なプロセスオプションが必要な場合は、お気軽にお問い合わせください。

再構成基板

キャリア基板上にSiダイを再配列し、樹脂封止を行います。

封止後、キャリア基板を剥離します。

再配線

絶縁層と銅再配線のパターニングを行い、再配線層を形成します。

はんだボール搭載

上層絶縁層、UBM層を形成し、その上にはんだボールを搭載します。

ダイシング(個片化)

ダイシングによって個片化したパッケージを、製品として納入します。

お問い合わせ・ダウンロード

お問い合わせ・ダウンロード

お問い合わせ

フォームが表示されるまでしばらくお待ち下さい。

恐れ入りますが、しばらくお待ちいただいてもフォームが表示されない場合は、こちらまでお問い合わせください。